Toolchain: PLECS (version 4.9.5) with imperix ACG target (SDK 2025.1), running on B-Box in simulation.

Blocks: CONFIG (CLOCK_0 = f_sw, Postscaler = 1), CB-PWM with Triangle carrier.

CONFIG.PWM → CB-PWM “>” (clock)

Phase(s) input enabled; my phase P ∈ [0,1) comes from a Triggered Subsystem that runs once per carrier period (triggered by CONFIG.Task).

I tried Single-rate and Double-rate for PWM parameters update rate.

Goal: my algorithm requires changing the carrier phase every carrier period (randomly among 0°, 90°, 180°, 270°).

What I expect

At each period boundary, when I jump the phase (e.g., from 0° to 90° or 180°), the carrier should instantaneously jump to the new phase index and then continue with the normal slope (no extra “fold” within the same period).

What I observe

When I jump the phase at the period boundary, the new phase does not take effect immediately. Instead, it seems to wait until the next carrier extremum (peak or valley) before continuing integration, leaving a missing segment.

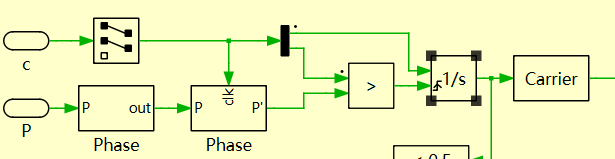

The image shows the internals of CB_PWM.

Questions

Is this just a simulation issue? Or does this also happen when generating code for FPGA?

Is this behavior expected from CB-PWM’s parameter sampling/locking semantics in PLECS/imperix ACG, or is it a known issue?

How can I guarantee the phase jump is applied exactly at the period boundary (i.e., no wait until the next peak/valley)?