Hi iam working on Dual active bridge converter as input as 45v and Output as 225 .

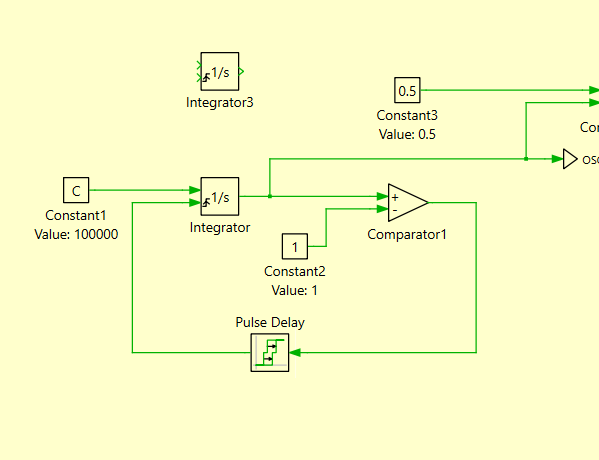

We have Developed the Control algorithm for This Requirement and its working fine.But we are unable to Generate Code as the error shows as your design has Algebraic Loop.

Is there any changes to make here .

Please find the Plecs File attached

DAB_3KW_PLECS_V1.plecs (124.1 KB)

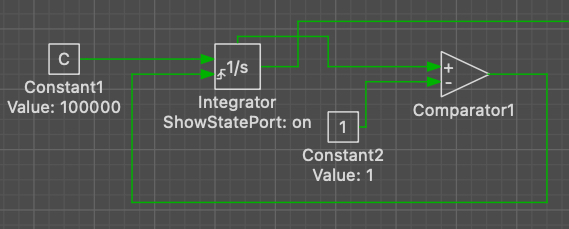

The warning message provides the suggested solution - “Use the integrator state port to avoid the algebraic loop”. You need to enable the “Show State Port” option in the integrator parameter. The advantage of using the state port vs. the pulse delay, is that the delay means the integrator will exceed the threshold before being reset where as the state will not.

An even simpler solution would be to enable wrapping within the integrator, with an upper limit of 1 and lower limit of 0, as that is essentially what your logic is doing. Again, this can be configured in the block mask. You can then remove the external comparator and reset logic.

Also, putting PID controllers between your modulation signal and gate driver doesn’t make much sense…